触发器的三种触发方式:1、电平触发;触发信号为有效电平(高或低)时,输入信号进入触发器电路,置触发器为相应状态。2、边沿触发,指的是接收时钟脉冲CLK 的某一约定跳变(正跳变或负跳变)来到时的输入数据。3、脉冲触发。

本教程操作环境:windows10系统、Dell G3电脑。

触发器的三种触发方式为:电平触发、边沿触发、脉冲触发。

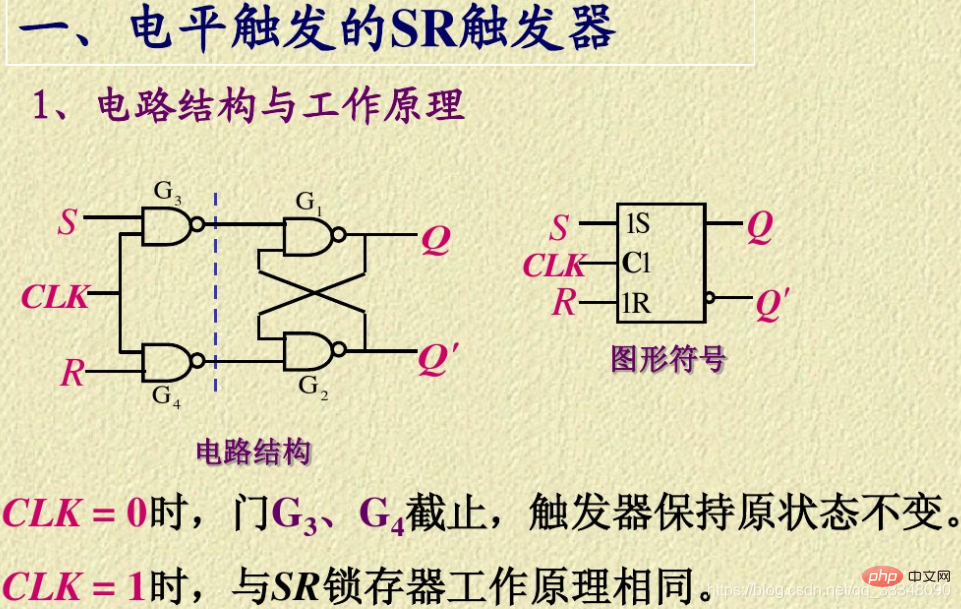

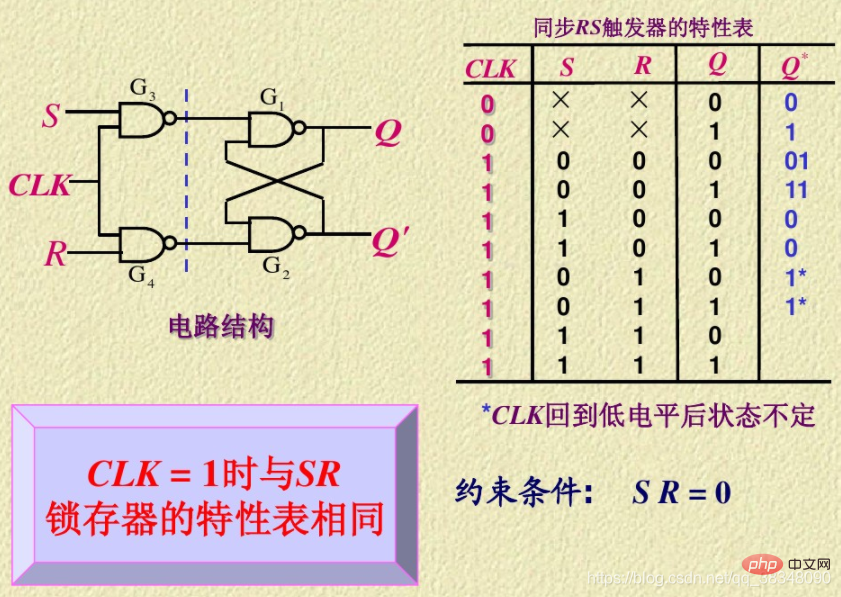

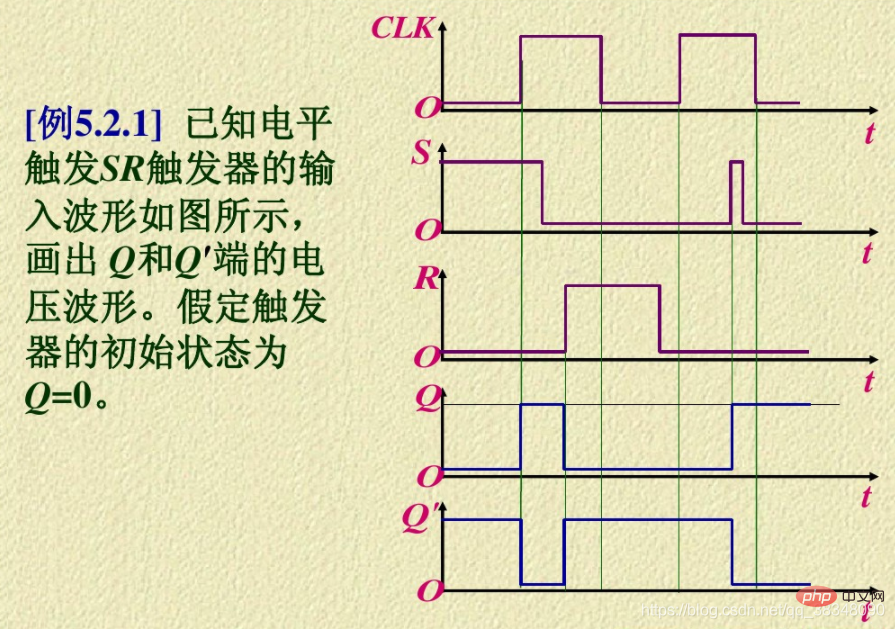

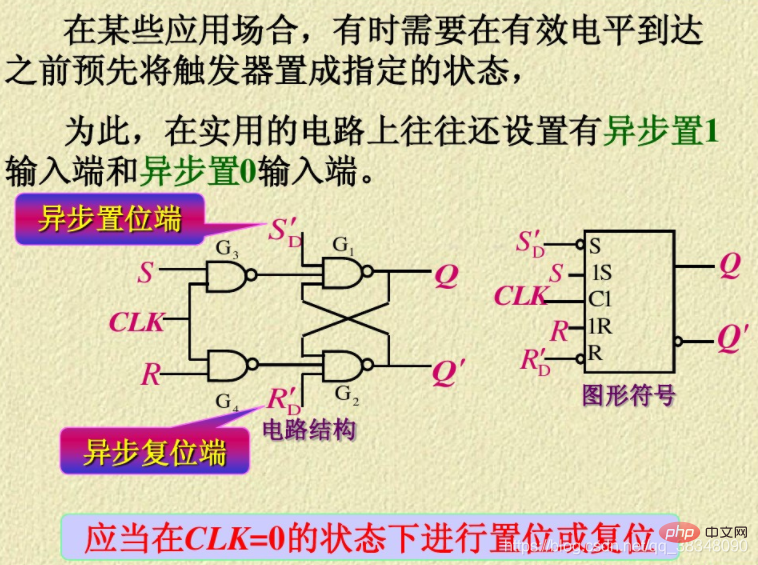

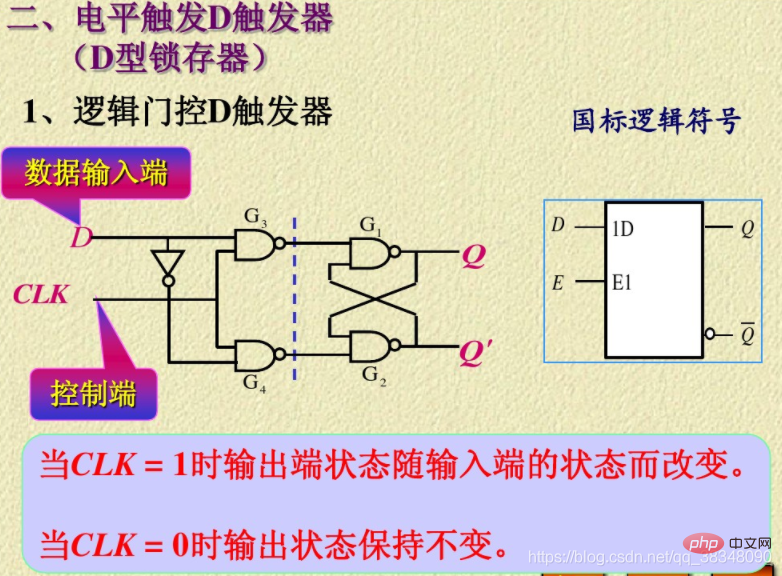

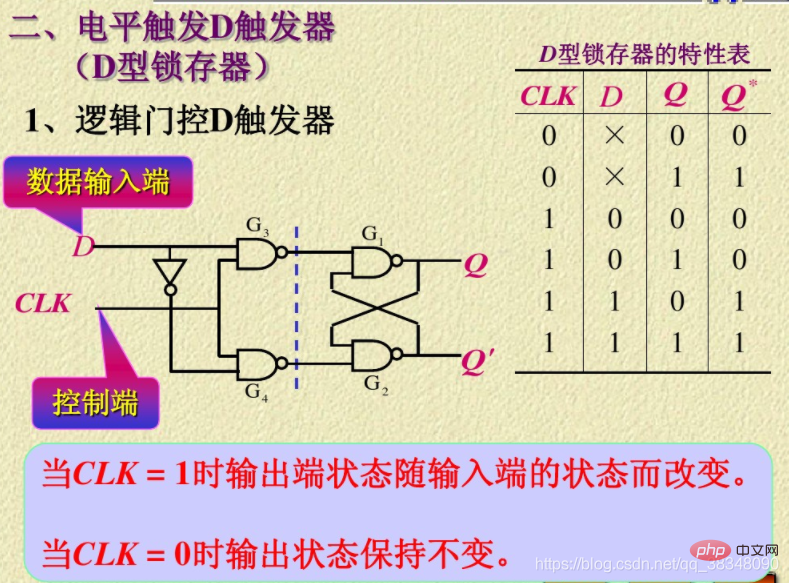

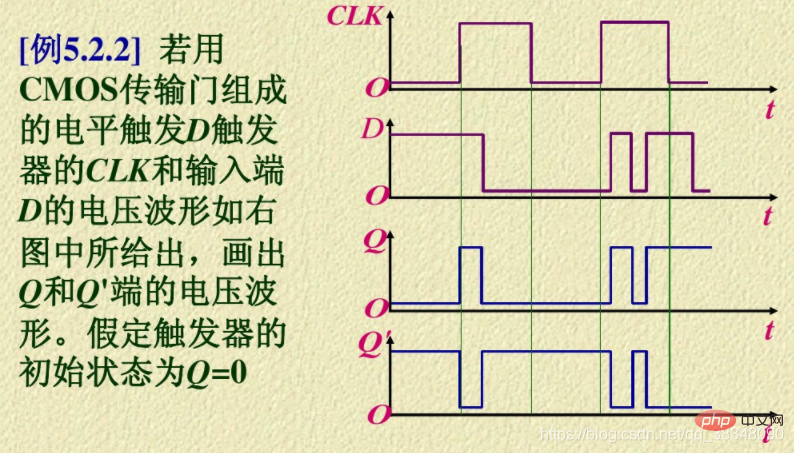

电平触发

触发信号为有效电平(高或低)时,输入信号进入触发器电路,置触发器为相应状态。触发信号变为无效电平后,输入信号被封锁,触发器状态保持。

状态随有效信号全过程改变。

**触发器种类:**电平触发的SR 触发器、电平触发的D触发器

电平触发的动作特点:

只有当CLK变为有效电平时,触发器才能接受输入信号,并按照输入信号将触发器置成相应的状态。

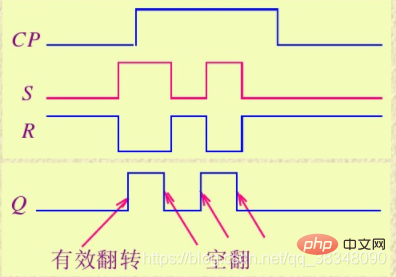

在CLK=1的全部时间里S、R的变化都将引起触发器输出端的状态变化。

如果CLK=1期间输入信号多次发生变化,则触发器的状态也会发生多次翻转。

这降低了电路的抗干扰能力。

在一个时钟脉冲周期里,触发器发生多次翻转的现象叫做空翻。

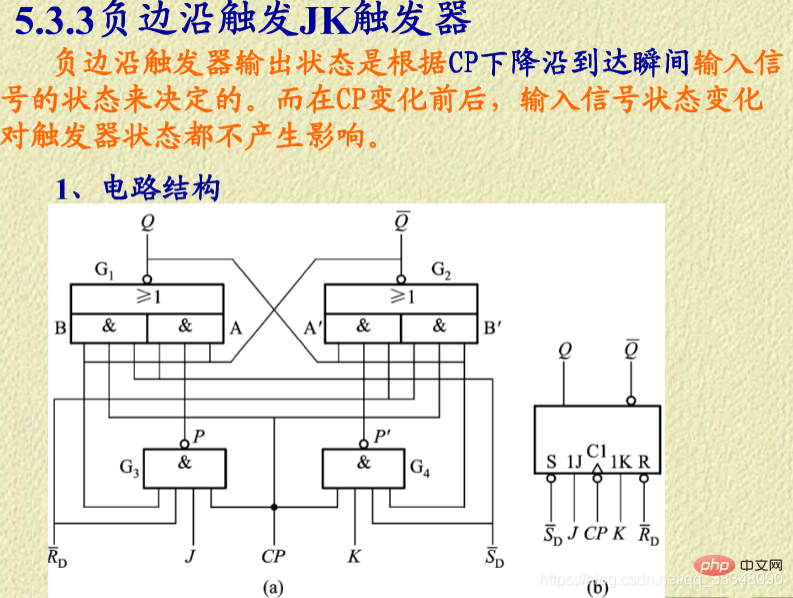

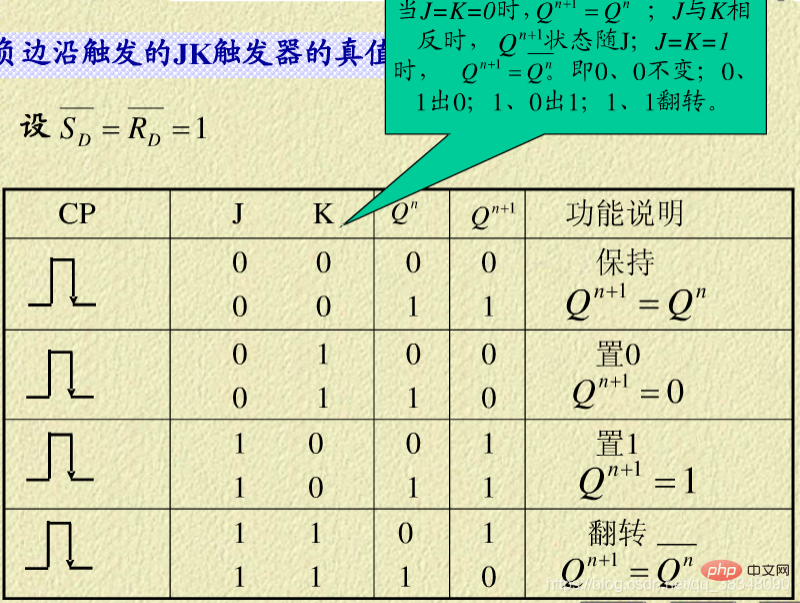

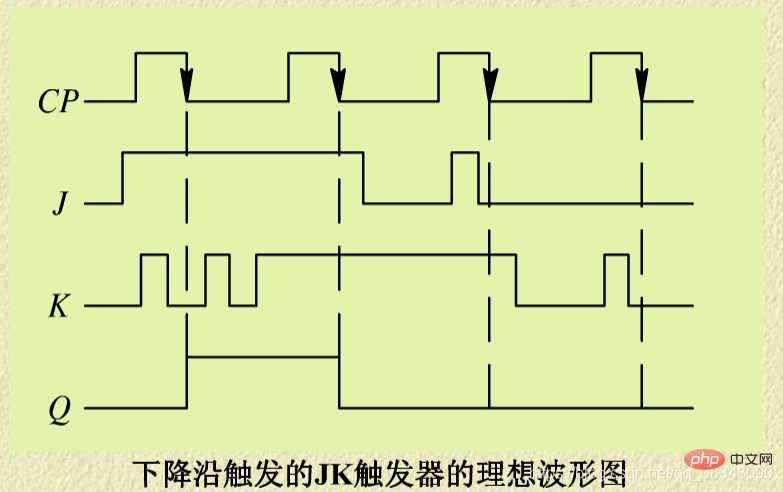

边沿触发

为了提高触发器的可靠性,增强抗干扰能力,希望触发器的此台仅仅取决于CLK信号的下降沿(或上升沿)到达时刻输入信号的状态,而在此之前和之后输入状态的变化对触发器的状态没有影响。

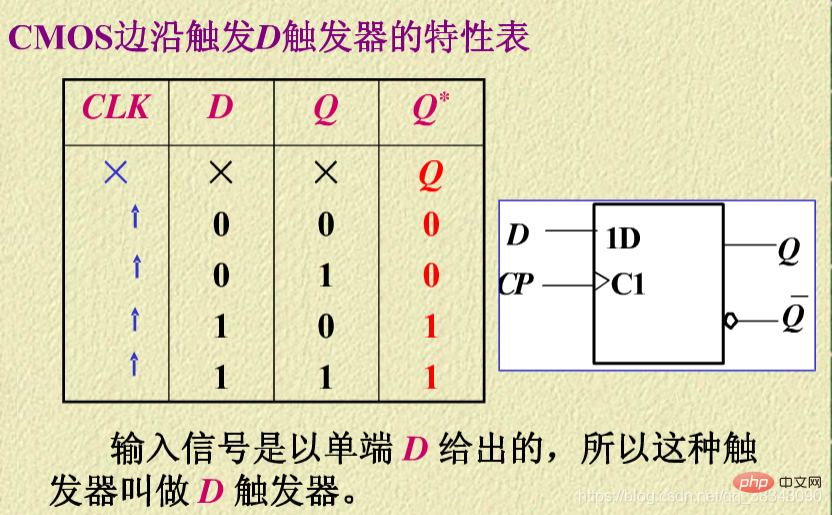

边沿触发指的是接收时钟脉冲CLK 的某一约定跳变(正跳变或负跳变)来到时的输入数据。在CLK=l 及CLK=0 期间以及CLK非约定跳变到来时,触发器不接收数据的触发器。

仅与该时刻的状态有关。

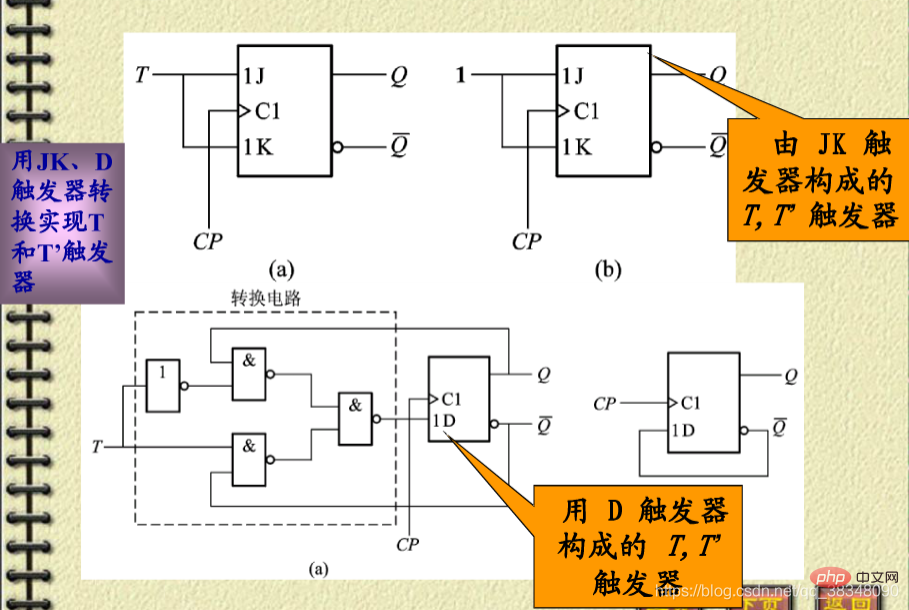

触发器种类:

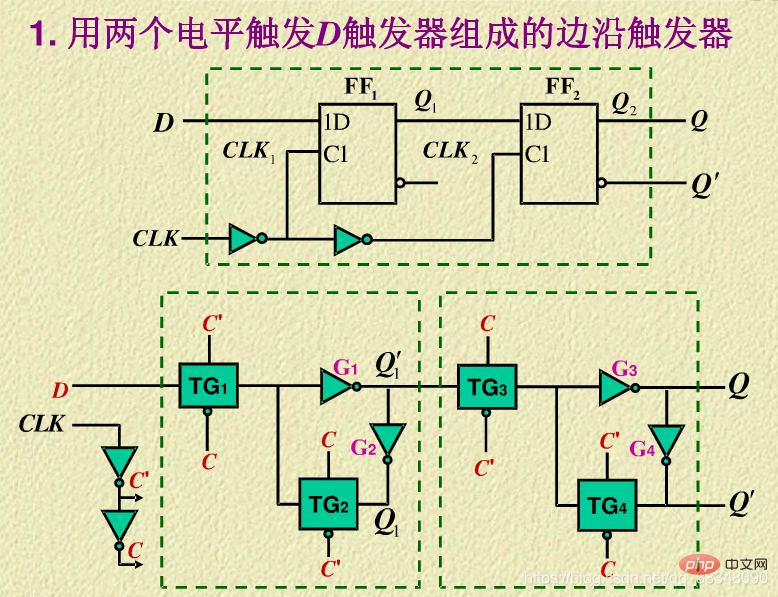

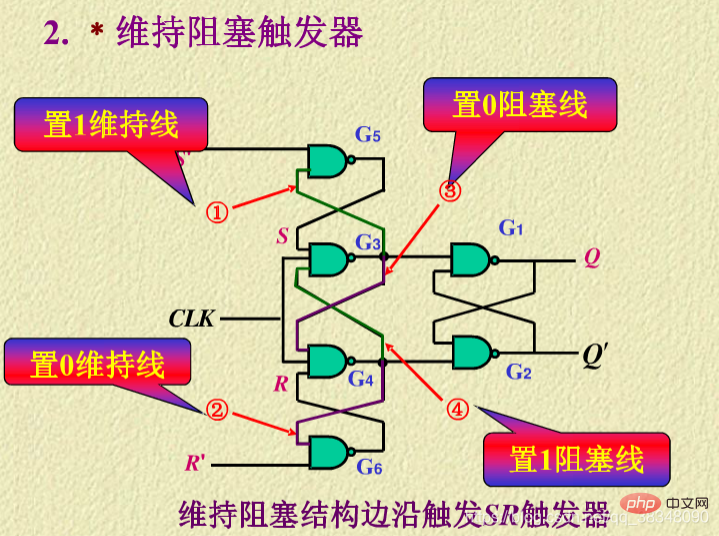

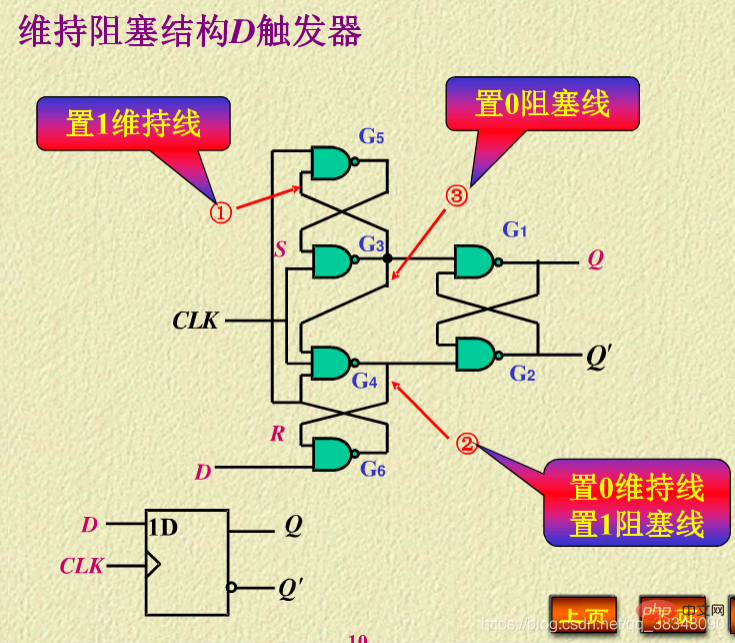

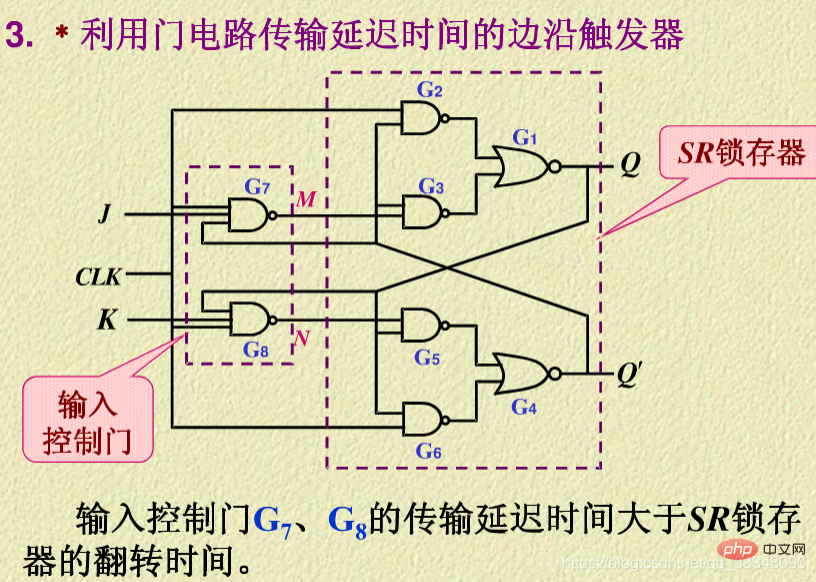

用两个电平触发D触发器构成的边沿触发器、维持阻塞触发器、利用门电路传输延迟时间的边沿触发器

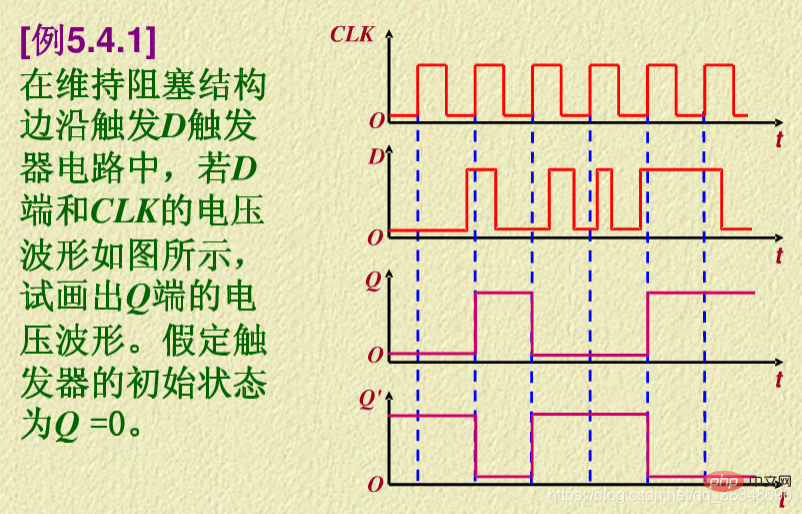

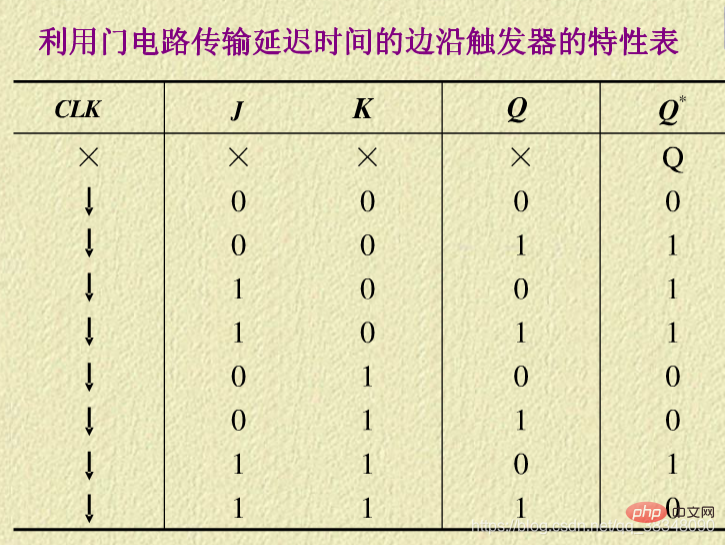

边沿触发方式的触发特点:

触发器的次态仅取决于时钟信号的上升沿(也称为正边沿)或下降沿(也称为负边沿)到达时输入的逻辑状态。而在以前和以后,输入信号的变化对触发器的输出状态没有影响。

这一特点有效地提高了触发器的抗干扰能力,因而也提高了工作可靠性。

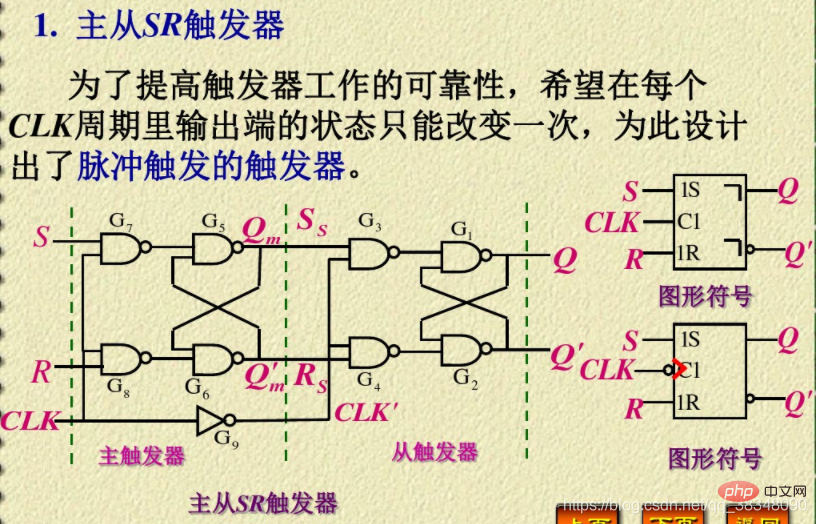

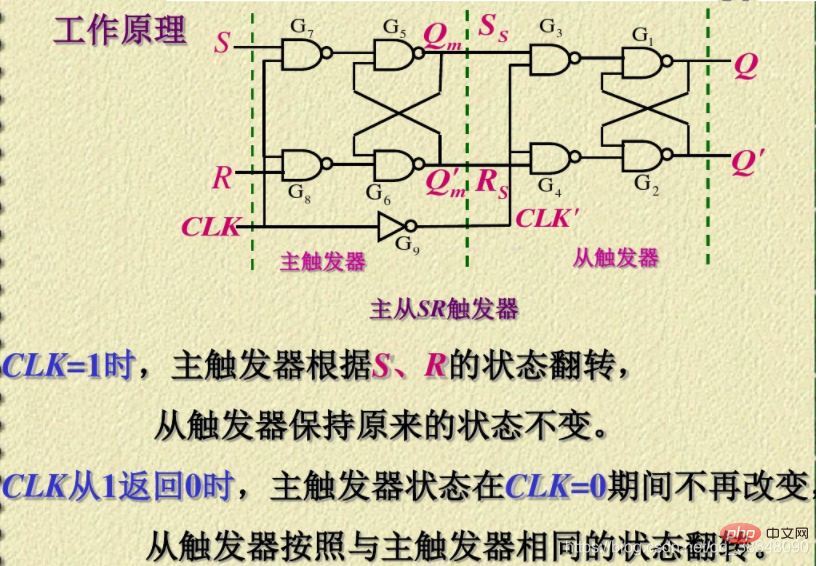

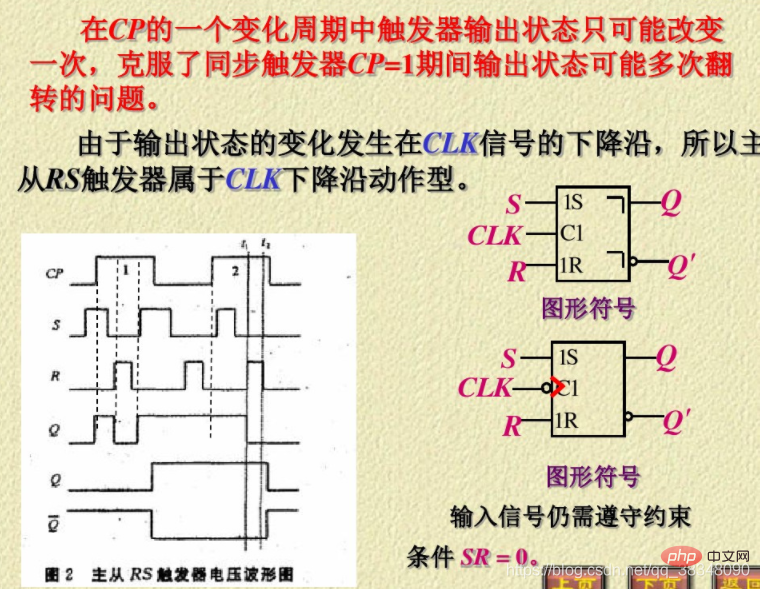

脉冲触发

常用主从结构实现,即主、从触发器串联,触发信号反相。以正脉冲触发为例,当触发信号为高时,输入信号进入主触发器,置主触发器状态;触发器变低后,输入信号被封锁,主触发器状态保持,同时,从触发器的状态根据主触发器状态确定。

信号只可能改变一次。

触发器种类:

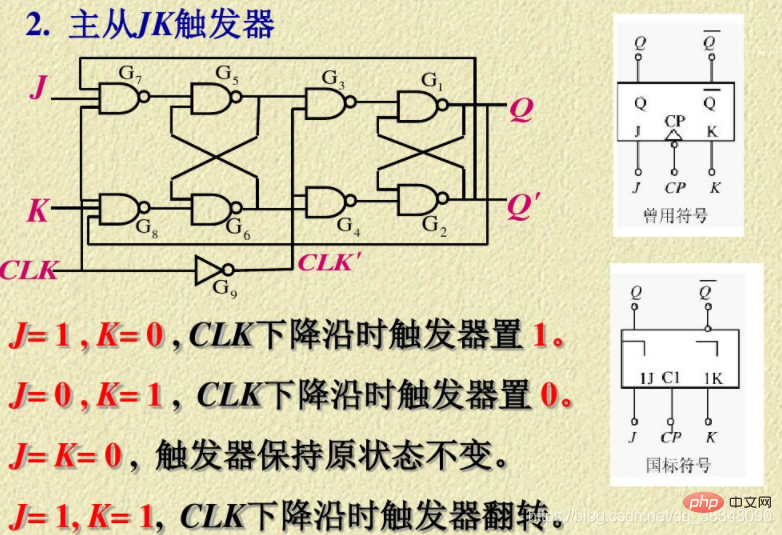

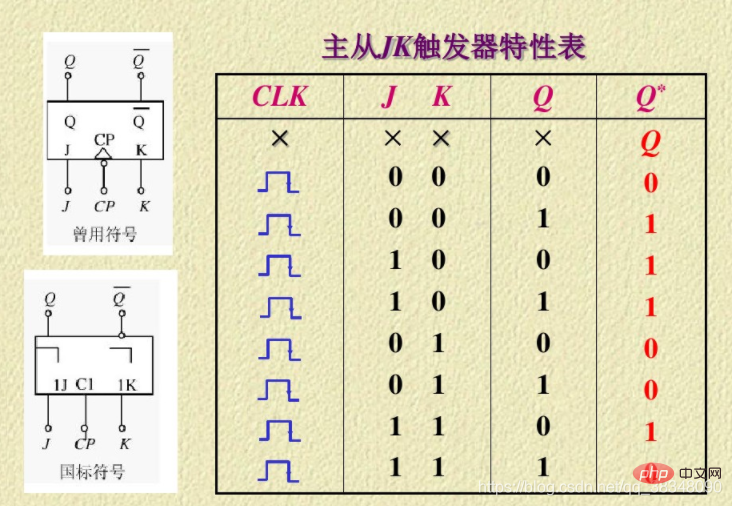

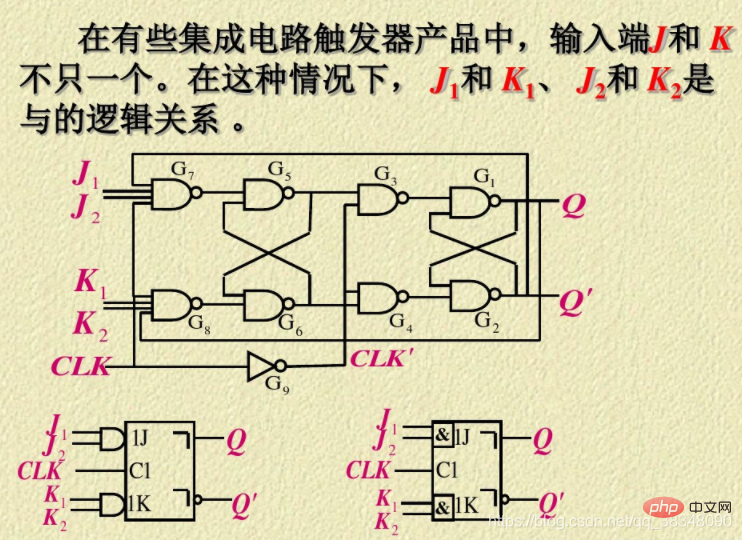

主从SR触发器、主从JK触发器

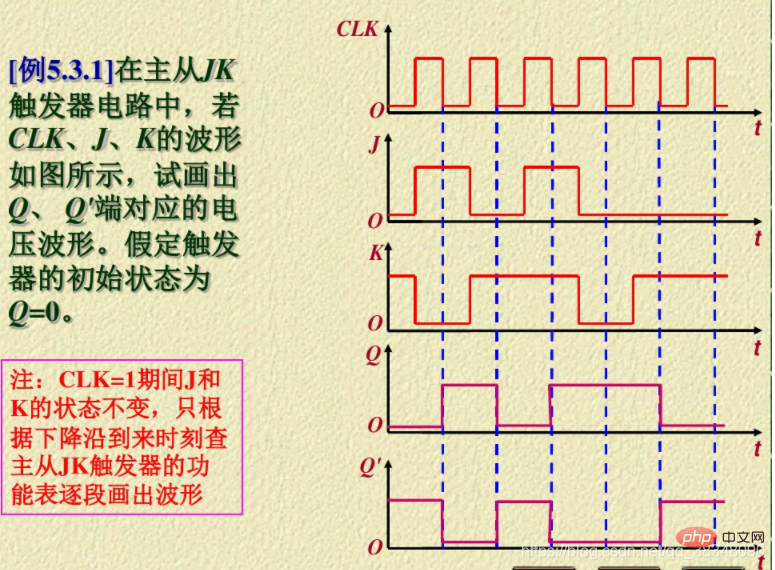

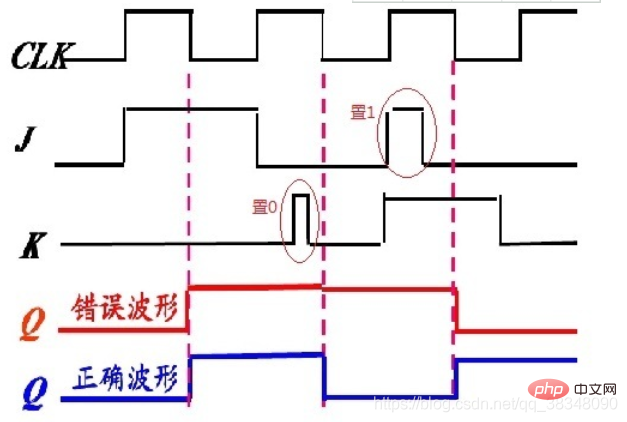

脉冲触发的动作特点:

1、触发器的翻转分两步动作。

第一步,在CLK=1期间主触发器接收输入端信号,而从触发器不动;

第二步,CLK下降沿到来时从触发器按照主触发器状态翻转,所以Q、Q’状态的变化发生在CLK的下降沿(若CLK以低电平为有效信号,则Q、Q’状态变化发生在CLK的上升沿)。

2、因为主触发器本身是电平触发SR触发器,所以在CLK=1的全部时间里输入信号都将对主触发器起控制作用。

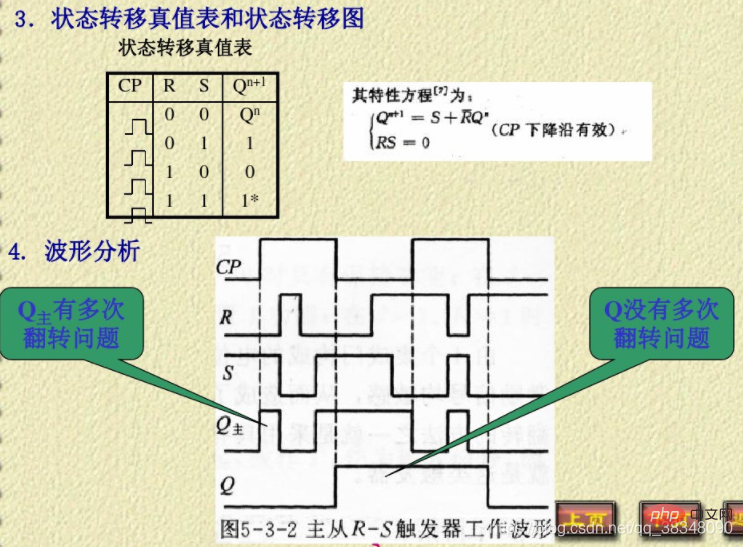

脉冲触发和边沿触发的区别:

脉冲触发的主从JK触发器,不能简单地以时钟下降沿时刻的 J、K 状态来判断 Qn+1 的状态,

如图,在时钟高电平期间,J、 K 的状态会改变有效时刻的逻辑关系,本来 J = K = 0 时,Q 是保持不变的。

可见脉冲触发的主从触发器容易受到干扰,不是实用的触发器,只是教材上介绍触发器的发展史,或者说触发器的原理、结构的一部分内容,知道有这么一回事即可。

站长资讯网

站长资讯网