1 月 19 日消息,据 BusinessKorea 报道,三星电子正在加快 3D DRAM 的研究和开发,这家半导体巨头已经开始加强相关团队建设,比如招聘人员。

过去,DRAM 是通过将晶体管和电容器排在一个平面上生产的。然而,随着 20 世纪 80 年代末 DRAM 容量超过 4 兆,提高 DRAM 的密度变得困难,使得重新排列电路和电容成为必然。当时,DRAM 行业分为“沟槽组”和“堆栈组”,前者选择将电路和储存器放在平面下,后者选择将它们堆积在平面上。

日本的东芝和 NEC 以及美国的 IBM 更倾向于沟槽法,而三星电子则选择堆叠法。当时,三星电子采用堆叠法是因为这是一种更容易制造 DRAM 和检查生产过程中问题的方法。因此,三星电子可以建立一个半导体帝国,并在大约 30 年的时间里一直保持其在 DRAM 市场上的第一地位。

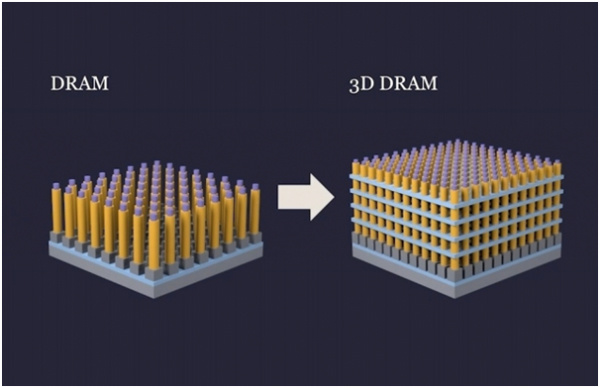

在堆叠法变得普遍之后,芯片制造商通过缩小单元尺寸或间距来提高 DRAM 的性能。然而,在有限的空间内增加单元的数量,他们遇到了物理限制。另一个问题是,如果电容器变得越来越薄,它们可能会坍塌。3D DRAM 的概念就是在这种背景下提出的,目前的 DRAM 可以被称为 2D DRAM。

据报道,三星电子已经开始开发一种躺着堆叠单元的技术。这是与高带宽内存(HBM)不同的概念,后者是通过将多个模具堆叠在一起产生的。

此外,三星电子还在考虑增加 DRAM 晶体管的栅极(电流门)和通道(电流路径)之间的接触面。这意味着三面接触的 FinFet 技术和四面接触的 Gate-all-around(GAA)技术可以用于 DRAM 生产。当栅极和通道之间的接触面增加时,晶体管可以更精确地控制电流的流动。

美光科技和 SK 海力士也在考虑开发 3D DRAM。美光提交了一份与三星电子不同的 3D DRAM 的专利申请。美光公司的方法是在不铺设单元的情况下改变晶体管和电容器的形状。Applied Materials 和 Lam Research 等全球半导体设备制造商也开始开发与 3D DRAM 有关的解决方案。

然而,由于开发新材料的困难和物理限制,3D DRAM 的商业化还需要一些时间。业内人士预测,3D DRAM 将在 2025 年左右问世。

特别提醒:本网信息来自于互联网,目的在于传递更多信息,并不代表本网赞同其观点。其原创性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容、文字的真实性、完整性、及时性本站不作任何保证或承诺,并请自行核实相关内容。本站不承担此类作品侵权行为的直接责任及连带责任。如若本网有任何内容侵犯您的权益,请及时联系我们,本站将会在24小时内处理完毕。

站长资讯网

站长资讯网